TUGAS 6 SISTEM BUS OLEH: PANDU 2103015025

Konsep Program

Pemrograman (hardware) merupakan proses penghubungan berbagai komponen logika pada konfigurasi yang diinginkan untuk membentuk operasi aritmatik dan logik pada data tertentu. Hardwired program tidak flexibel. General purpose hardware dapat mengerjakan berbagai macam tugas tergantung sinyal kendali yang diberikan. Daripada melakukan re-wiring, Lebih baik menambahkan sinyal-sinyal kendali yang baru.

Pengertian Program

Program adalah suatu deretan langkah-langkah.

Pada setiap langkah, dikerjakan suatu operasi arithmetic atau logical.

Pada setiap operasi, diperlukan sejumlah sinyal kendali tertentu.

Fungsi Control Unit

Untuk setiap operasi disediakan kode yang unik.

Contoh: ADD, MOVE.

Bagian hardware tertentu menerima kode tersebut kemudian menghasilkan sinyal-sinyal kendali.

Komponen yang Diperlukan

Control Unit (CU) dan Arithmetic and Logic Unit (ALU) membentuk Central Processing Unit (CPU)

Data dan instruksi harus diberikan ke sistem dan dikeluarkan dari sistem

Komponen: Input/output

Diperlukan tempat untuk menyimpan sementara kode instruksi dan hasil operasi.

Komponen: Main memory

Siklus Instruksi

Fetch Cycle

Program Counter (PC) berisi address instruksi berikutnya yang akan diambil.

Processor mengambil instruksi dari memory pada lokasi yang ditunjuk oleh PC.

Instruksi dimasukkan ke Instruction Register (IR).

Processor menginterpret dan melakukan tindakan yang diperlukan.

Execute Cycle

1. Processor-memory

Transfer data antara CPU dengan main memory.

2. Processor I/O

Transfer data antara CPU dengan I/O module.

3. Data processing

Operasi arithmetic dan logical pada data tertentu.

4. Control

Mengubah urutan operasi.

Contoh: jump

5. Kombinasi di atas.

Diagram Keadaan Siklus Instruksi

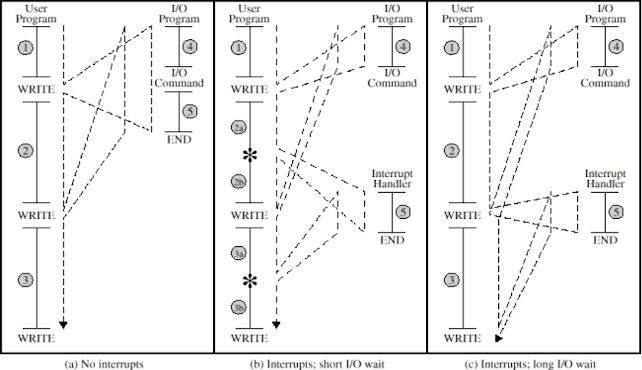

Suatu mekanisme yang disediakan bagi modul-modul lain (mis. I/O) untuk dapat meng-interupsi operasi normal CPU.

1. Program

Misal: overflow, division by zero.

2. Timer

Dihasilkan oleh internal processor timer.

Digunakan dalam pre-emptive multi-tasking.

3. I/O

4. Hardware failure

Misal: memory parity error.

Ada beberapa kemungkinan interkoneksi sistem

Yang biasa dipakai: Single Bus dan multiple BUS

PC: Control/Address/Data bus

DEC-PDP: Unibus

Pengertian Bus

Jalur komunikasi yang menghubungkan beberapa device

Biasanya menggunakan cara broadcast

Seringkali dikelompokkan

Satu bus berisi sejumlah kanal (jalur)

Contoh bus data 32-bit berisi 32 jalur

Jalur sumber tegangan biasanya tidak diperlihatkan

Data Bus

Membawa data.

Tidak dibedakan antara “data” dan “instruksi”.

Lebar jalur menentukan performance: 8, 16, 32, 64 bit.

Address Bus

Menentukan asal atau tujuan dari data.

Misalkan CPU perlu membaca instruksi (data) dari memori pada lokasi tertentu.

Lebar jalur menentukan kapasitas memori maksimum dari sistem.

Contoh 8080 memiliki 16 bit address bus maka ruang memori maksimum adalah 64k.

Control Bus

Informasi kendali dan timing.

Sinyal read/write memory (MRD/MWR).

Interrupt request (IRQ).

Clock signals (CK).

Skema Interkoneksi Bus

1. Dedicated

Jalur data & address terpisah

2. Multiplexed

Jalur bersama

Address dan data pada saat yg beda

Keuntungan: jalur sedikit

Kerugian:

Kendali lebih komplek

Mempengaruhi performance

Arbitrasi Bus

Beberapa modul mengendalikan bus

Contoh CPU dan DMA controller

Setiap saat hanya satu modul yg mengendalikan

Arbitrasi bisa secara centralised atau distributed

Arbitrasi Centralized

Ada satu hardware device yg mengendalikan akses bus

Bus Controller

Arbitrer

Bisa berupa bagian dari CPU atau terpisah

Arbitrasi Distributed

Setiap module dapat meng-klaim bus.

Setiap modules memiliki Control logic.

Bus PCI

Peripheral Component Interconnection

Dikeluarkan oleh Intel sebagai public domain

32 atau 64 bit

50 Jalur

Jalur Bus PCI yang Wajib

1. Jalur System

Clock and reset

2. Address & Data

32 jalur multiplex address/data

3. Jalur validasi

4. Interface Control

5. Arbitrasi

Not shared

Direct connection to PCI bus arbiter

6. Error lines

Jalur Bus PCI yang Opsional

1. Interrupt lines

Not shared

2. Cache support

3. 64-bit Bus Extension

Additional 32 lines

Time multiplexed

2 lines to enable devices to agree to use 64-bit transfer

4. JTAG/Boundary Scan

For testing procedures

Command pada PCI

1. Transaksi antara initiator (master) dg target

2. Master pegang kendali bus

3. Master menentukan jenis transaksi

Misal I/O read/write

4. Fase Address

5. Fase Data

Soal dan Jawaban

1. Yang bukan bagian dari siklus instruksi adalah

a. Halt

b. Fetch Next Instruction

c. Execute Instruction

d. Mutate Instruction

2. Yang bukan bagian dari siklus eksekusi adalah

a. Mutator

b. Processor memory

c. Processor I/O

d. Control

3. Yang bukan bagian dari komponen CPU adalah

a. PC

b. IR

c. MAR

d. OPR

4. Yang bukan merupakan jenis bus adalah

a. Single Bus

b. Upper Bus

c. Unibus

d. Multiple Bus

5. Salah satu problem pada single bus adalah

a. Data overflow

b. Propagation delay

c. Short circuit

d. Instant propagation

6. Yang bukan merupakan bagian dari interrupt adalah

a. Program

b. Parity Comparator

c. I/O

d. Hardware failure

7. Berikut ini yang merupakan jenis bus adalah

a. Dedicated dan Uniplexed

b. Undedicated and Multiplexed

c. Dedicated dan Multiplexed

d. Undedicated and Uniplexed

8. Jalur pada Bus PCI yang opsional adalah

a. Address and Data

b. Arbitrasi

c. JTAG

d. Jalur System

9. Arbitrasi bus bisa secara ... atau ...

a. Centralized, Distributed

b. Node, Distributed

c. Recursively distributed, Multi-node

d. Decentralized, Distributed

10. Jalur Bus PCI yang wajib adalah

a. Interface Control

b. Interrupt Lines

c. Cache Support

d. Boundary Scan

Komentar

Posting Komentar